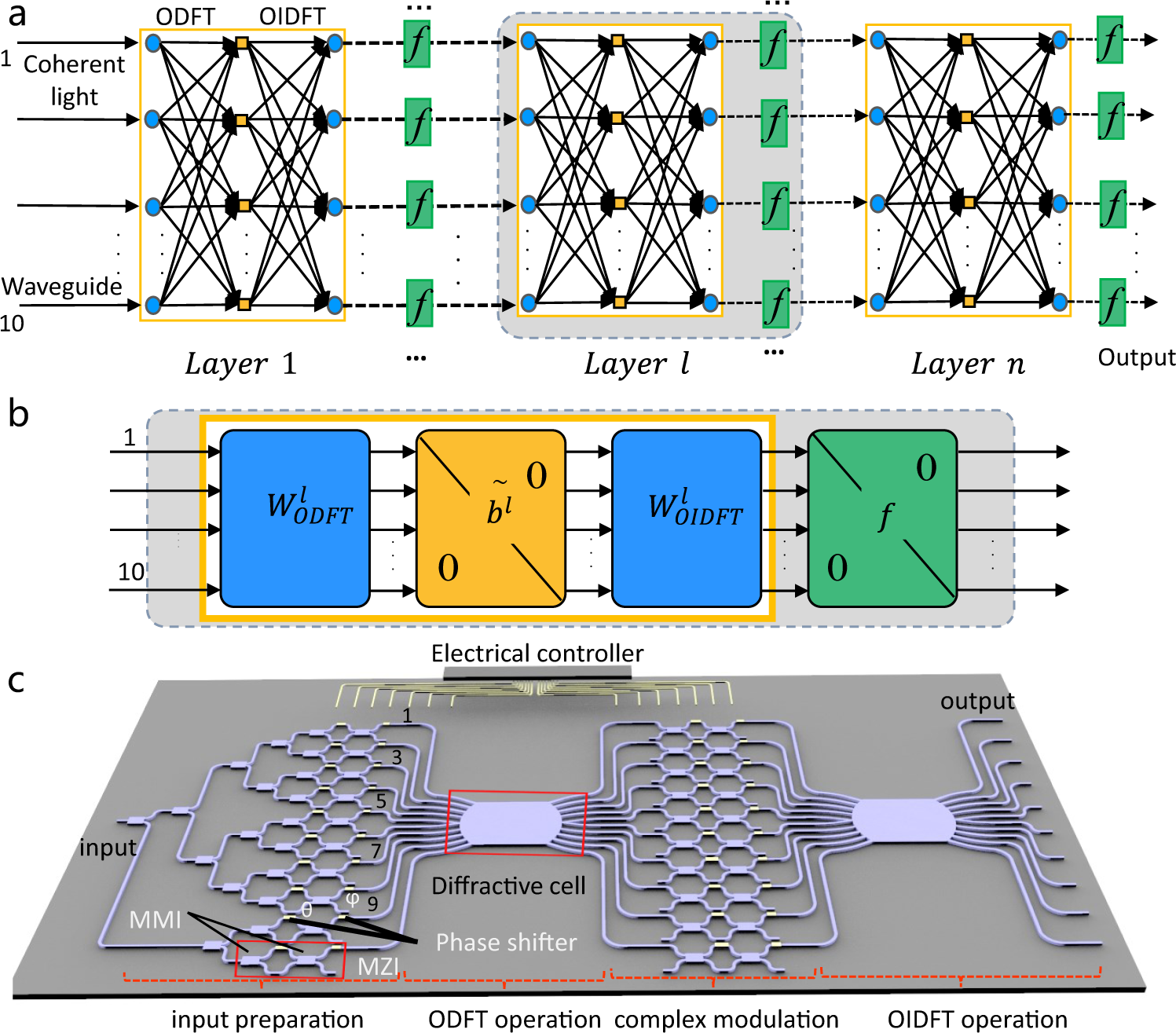

Space-efficient optical computing with an integrated chip diffractive neural network | Nature Communications

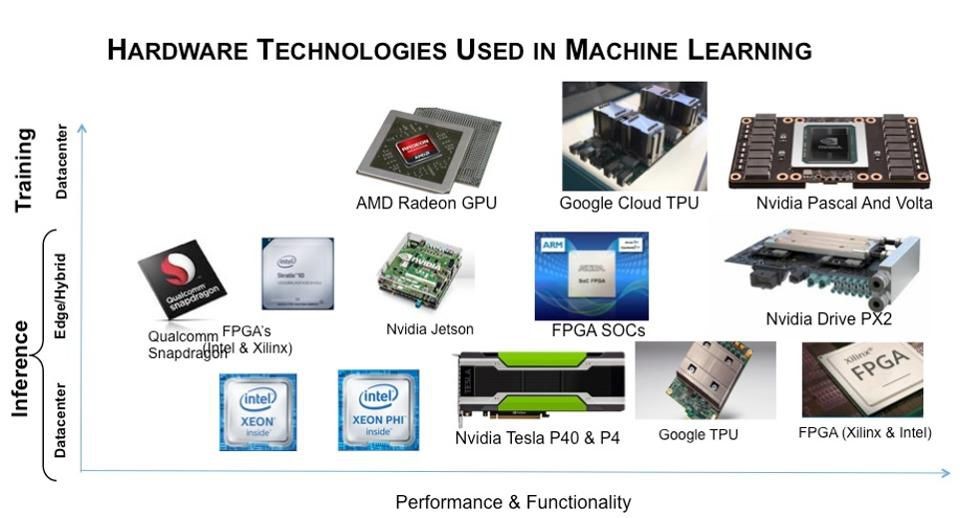

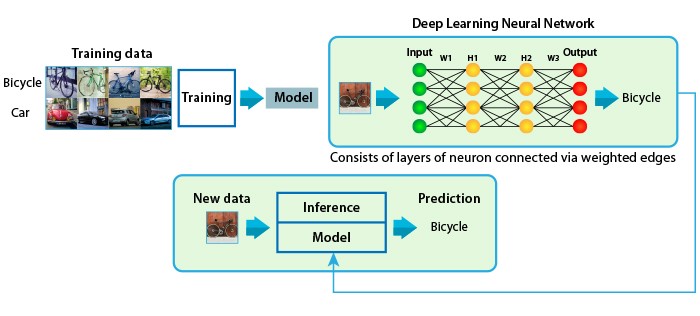

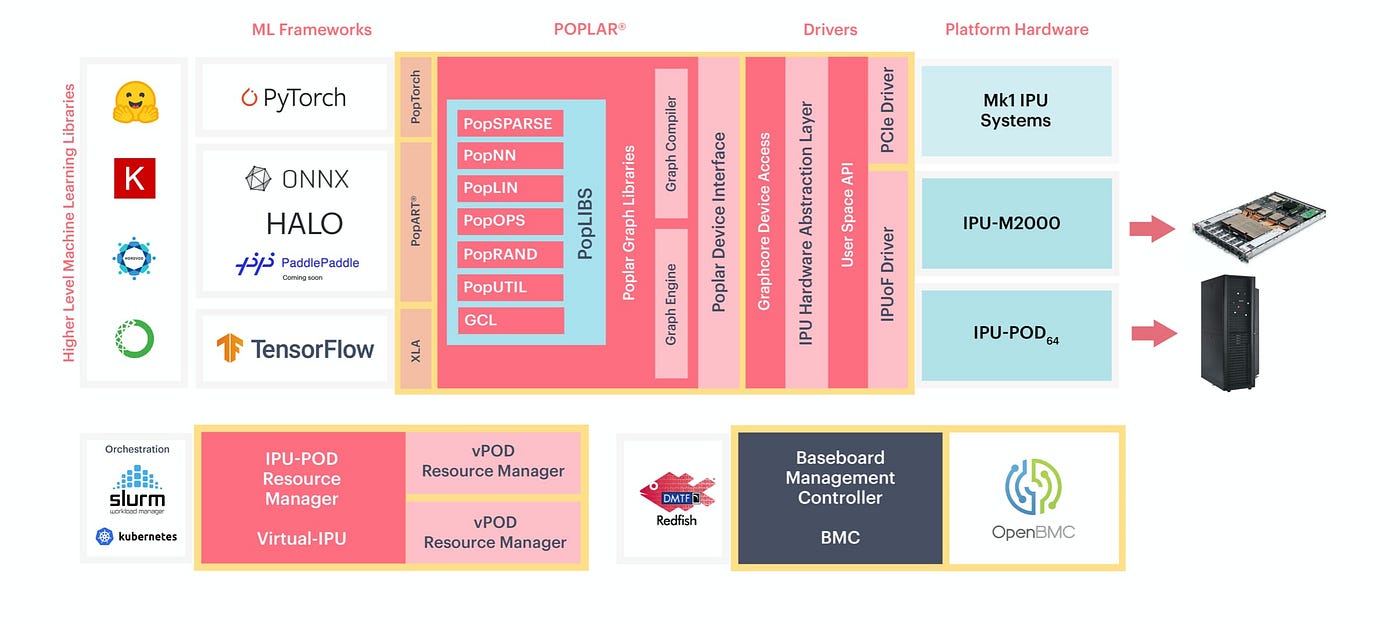

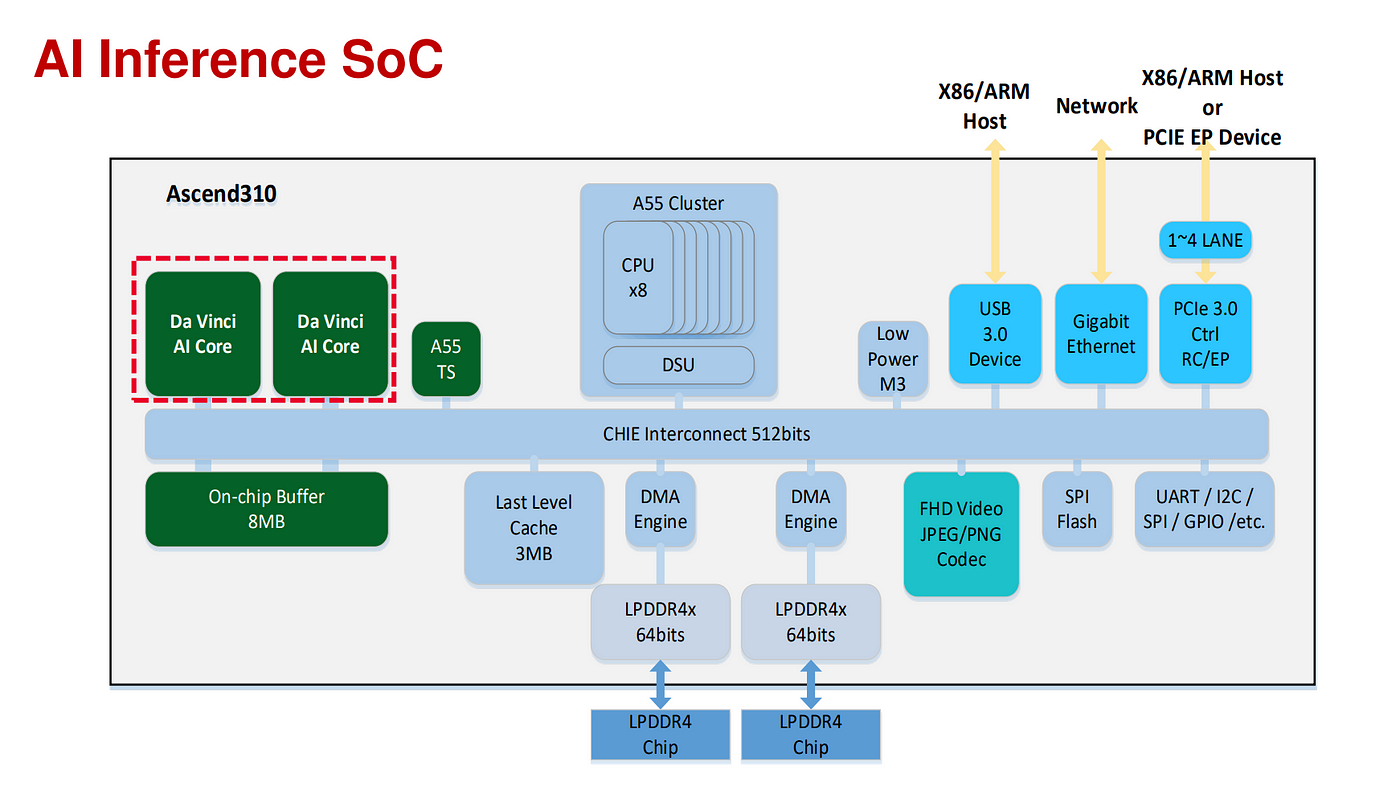

The Deep Learning Inference Acceleration Blog Series — Part 2- Hardware | by Amnon Geifman | Towards Data Science

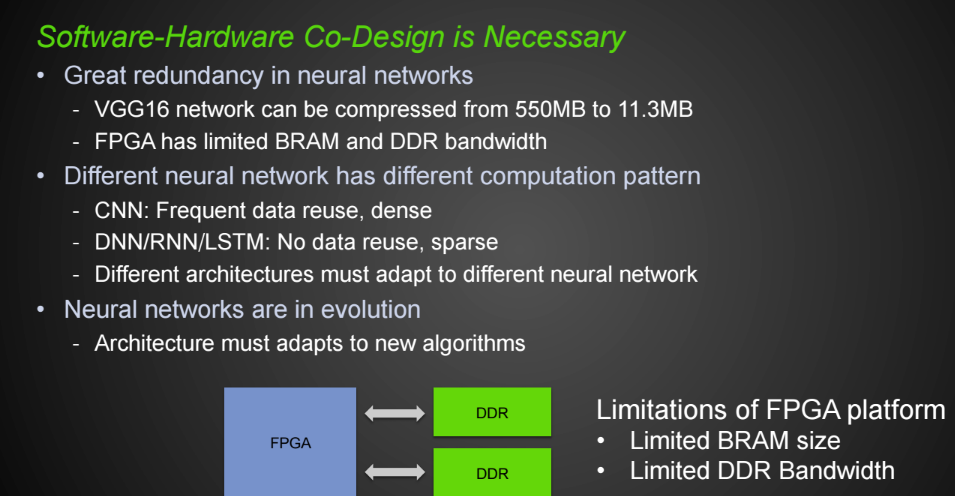

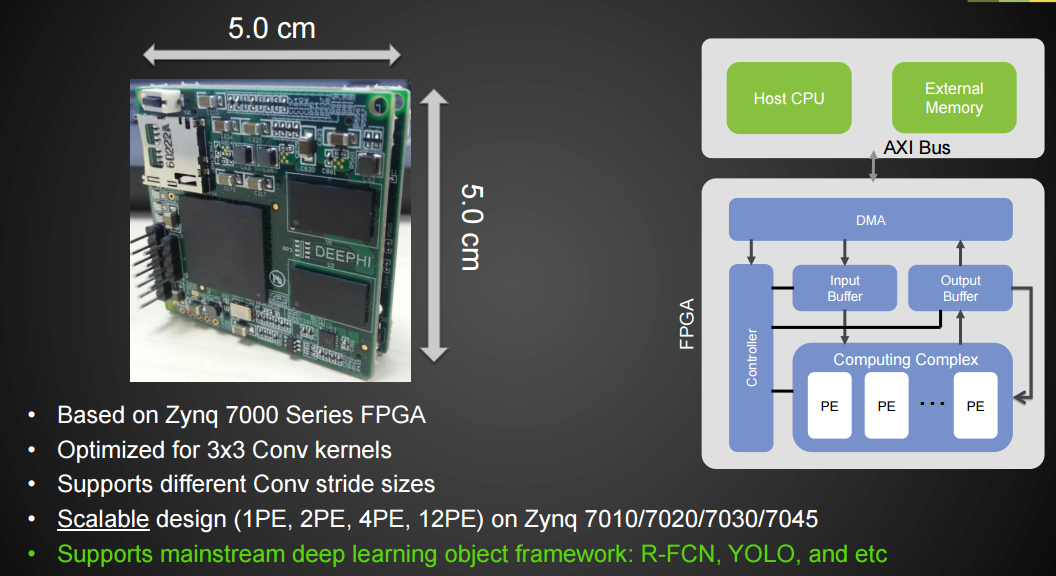

Applied Sciences | Free Full-Text | MLoF: Machine Learning Accelerators for the Low-Cost FPGA Platforms

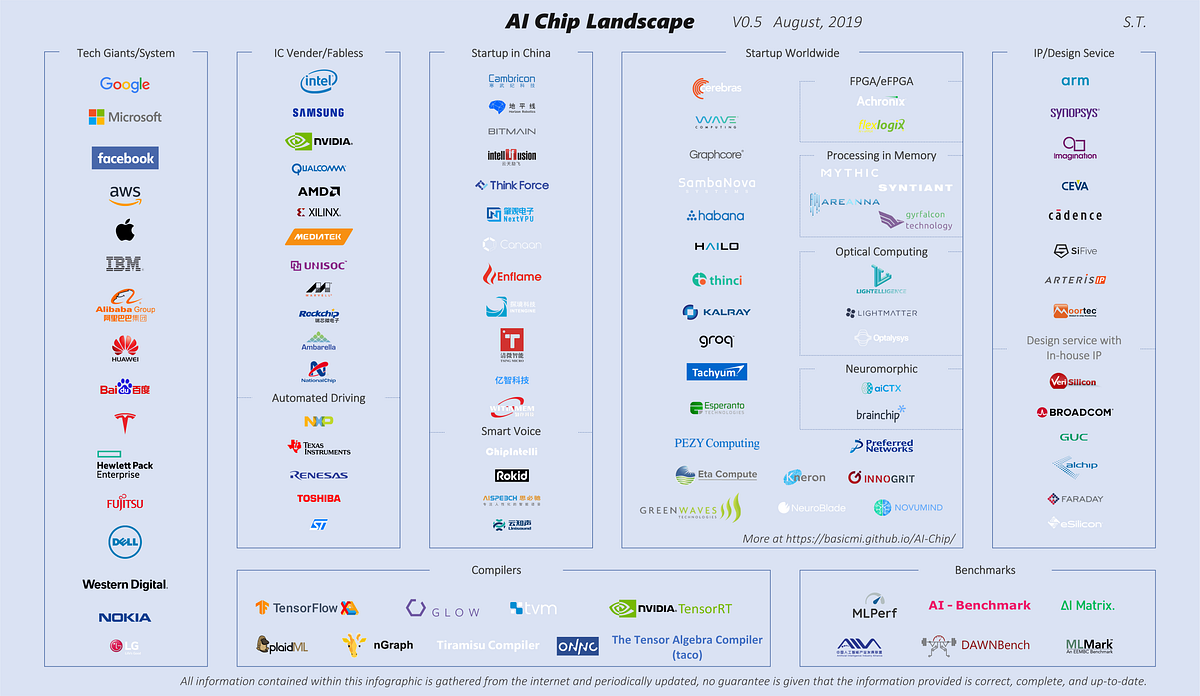

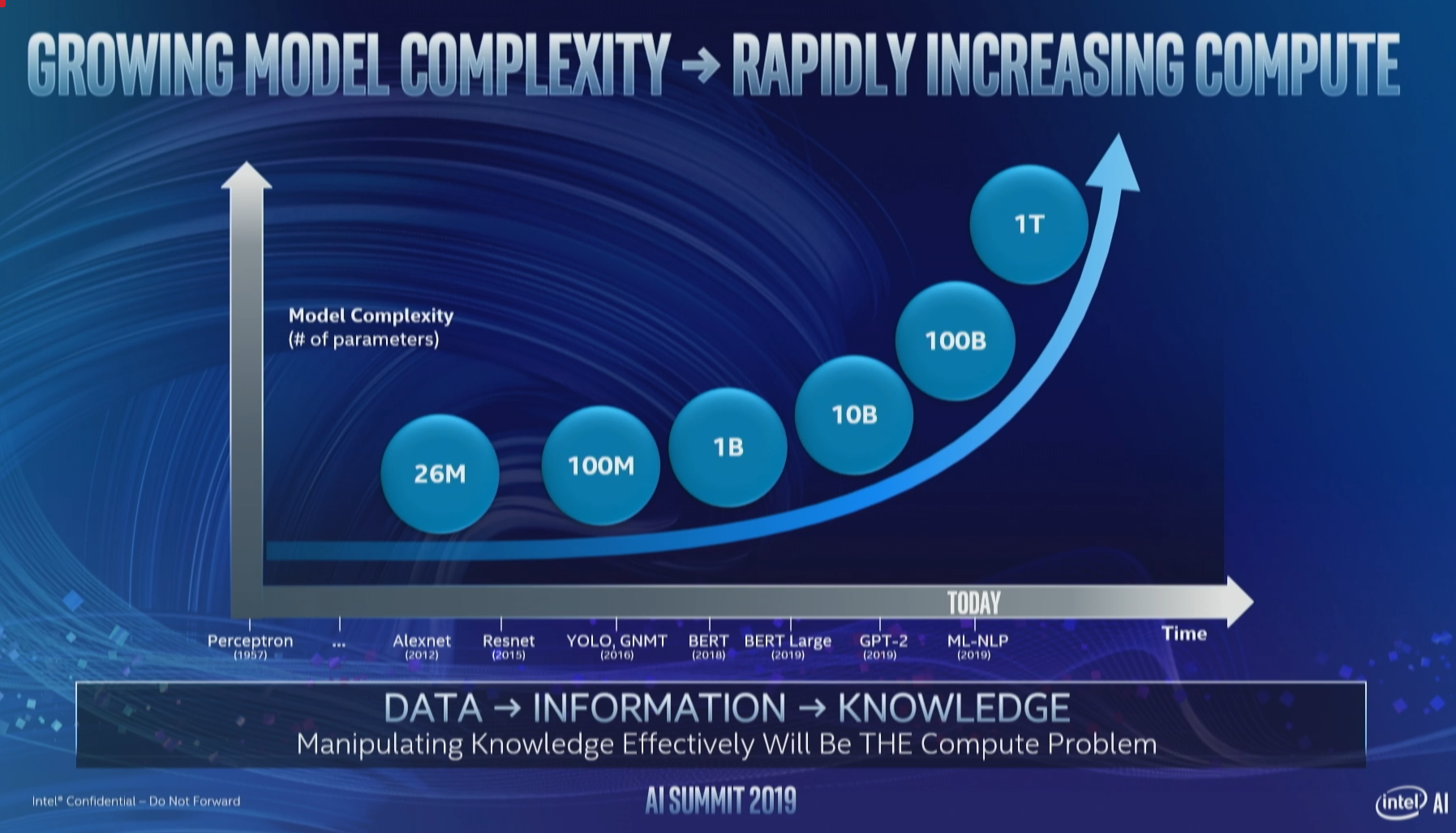

Intel Nervana Neural Network Processors (NNP), premiers ASICs conçus pour l'IA et le Deep Learning – DCmag

Deep Neural Network ASICs The Ultimate Step-By-Step Guide: Gerardus Blokdyk: 9780655403975: Textbooks: Amazon Canada